|

|

| プログラム位置づけ | プログラムの概要 | 各研究開発項目 | 課題推進者向け情報 |

|

|||||

|

プロジェクトマネージャー 小林和淑 (京都工芸繊維大学電気電子工学系教授/京都半導体共創ラボ長) |

|

|

| ・ | 2026年度からPIが増強されました。 ~2025年度までの前半3年間の14名のPIに加えて、6名のPIが新たに加わりました。 うち2名はスタートアップの所属。 |

|

| ・ | 量子ビット制御装置の長時間安定動作を実証 本プロジェクトの三好健文PIらの研究開発グループにより、超伝導量子ビットの制御に用いるマイクロ波信号の長時間安定化を実現する量子ビット制御装置 「QuEL-1 SE」 を開発し、その性能を実験的に実証しました。 詳細は、下記のプレスリリースをご覧ください。 https://qiqb.osaka-u.ac.jp/newstopics/pr20260327 https://prtimes.jp/main/html/rd/p/000000003.000173953.html |

|

| ・ | 三好 健文 PI(キュエル株式会社)が、31st Asia and South Pacific Design Automation Conference (APC-DAC 2026)

にて基調講演を行いました。 Keynote VI : Thursday, January 22, 09:05-09:50 "Design and Implementation of Control System for Quantum Computers" |

|

|

||

| ・ | 京都工芸繊維大学・新谷研究室の修士課程の学生である Zhipeng Liang君がIEEE SOCC 2025のStudent Paper Contest で"First Place"を受賞しました。 "Cryogenic Characterization and Compact Modeling of Forwad Body-Bias Effects in 180 nm Bulk CMOS Transistors", Zhipeng Liang, Shin Taniguhi, Hajime Takayama and Michihiro Shintani |

|

| ・ | 京都工芸繊維大学、2025年度オープンキャンパスが8月8日、9日に開催されました。 京都工芸繊維大学 電子システム工学専攻 集積システム講座 公開研究室(研究室見学) 及び 当プロジェクト(QUBECS)に参画するキュエル株式会社の制御装置の展示・説明が実施されました。 オープンキャンパス風景は、=> こちら |

|

| ・ | 小林和淑教授が半導体設計を教える日本の大学教員代表3人のうちの1人として紹介されました。 Yahoo News: 「日本半導体の復活を願うなら、半導体設計にせめて1000億円支援を」 2025年8月1日 https://news.yahoo.co.jp/expert/articles/ec907151e92e7538beeb2df1530333ba2d1ec211 |

|

| ・ | 本プロジェクトの成果の一部が「純国産の量子コンピュータ」として公開されました。 https://www.youtube.com/watch?v=dy_eBN4iSCs 2025年7月29日 |

|

| ・ | 『純国産・量子コンピュータ、7月28日稼働!』 万博会場からクラウド接続し、来場者に新しい“量子体験”も ムーンショット目標6 「スケーラブルな高集積量子誤り訂正システムの開発」、QUBECS (プロジェクトマネージャー:小林和淑) が研究支援、同プロジェクトQUBECSに参画しているキュエル社が開発した最新制御装置を採用。 ※大阪大学、量子情報・量子生命研究センター(QIQB)より発表 (2025年7月28日) https://qiqb.osaka-u.ac.jp/newstopics/pr20250728 |

|

| ・ | 2025年5月19日、日経XTECHに、量子コンピューターの制御装置や中継器を開発・販売する本プロジェクトの一員でもある、キュエル㈱の活躍ぶりが掲載されました。 https://xtech.nikkei.com/atcl/nxt/mag/ne/18/00001/00523/ |

|

| ・ | 2025年5月13日、14日で東京大学 VDEC で開催されたシステムとLSIのワークショップ2025で 新谷PIの研究室のZhipeng Liang

君(M1)が研究成果を発表し、優秀ポスター賞を受賞しました。 https://pdf.gakkai-web.net/ieice/icd/doc/poster_program_2025v3.pdf |

|

| ・ | COOL Chips 28のパネル討論"Sustainable AI: Emerging Architectures, Devices, and Quantum

Computing Towards Future Computing"に、小林PMがパネリストとして参加しました。 (2025年4月17日) スライドはこちら |

|

| ・ | 本プロジェクトの一端を担っているになっている、キュエル株式会社が量子コンピューターの命運握る制御装置を開発しました。 (2025年3月24日掲載) 詳細はこちら |

|

| ・ | IEICE総合大会にて企画セッション「量子コンピューティングの潮流:回路・デバイスからアプリケーションまで」 が開催されました。 (2025年3月26日) 詳細はこちら |

|

| ・ | ソシオネクストがGoogle Quantum AIと戦略的パートナーシップ、量子制御チップ開発 (2025年2月27日) 日経XTECHが報道。 詳細はこちら *本件は、本プロジェクトとは関係ございません。 |

|

| ・ | 低温工学・超電導学会 関西支部2024年度第 3 回講演会にて小林PMが講演 (2025年2月5日) 第3回講演会の詳細はこちら |

|

| ・ | 小林PMが委員長の応用物理学会超集積エレクトロニクス産学連携委員会第11回研究会 「量子コンピュータ最前線」開催(2025年1月20日)。 第11回研究会の詳細はこちら |

|

| ・ | 土谷 亮 准教授(滋賀県立大学)が、豊橋技術科学大学 Green-niX シンポジウムにて、大学生・高専生向けに集積回路研究の紹介として「集積回路設計の先端研究とこれから」

を講じました。(2024年9月26日) 案内サイト |

|

| ・ | 小林PMが、Quest-2024にて基調講演を行いました。 (2024年9月9日) スライドは下記の対外発表成果リストに掲載しております。 |

|

| ・ | サイトビジット 2024 (2024年7月30日実施) |

|

| ・ | Nature に掲載: Nature Focal Point on Quantum computing in Japan (特集トップページ) "Quantum computers shoot for the moon" (当プロジェクト: QUBECS) |

|

| ・ | APS TV March meeting 2024でのプロジェクト紹介動画 |

|

| ・ | 2021年4月23日開催 ムーンショット目標6 国際シンポジウム (Zoom Webinar) (公開動画) |

|

| * 対外発表成果リスト |

| プログラムの位置づけ |

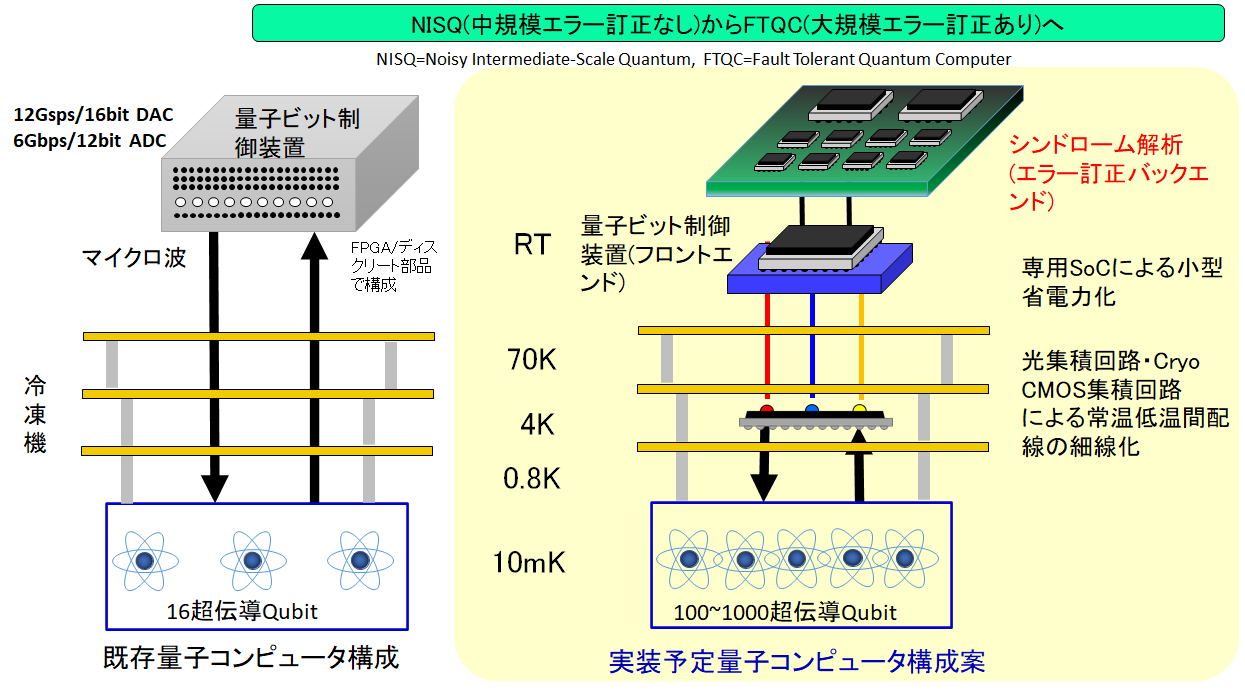

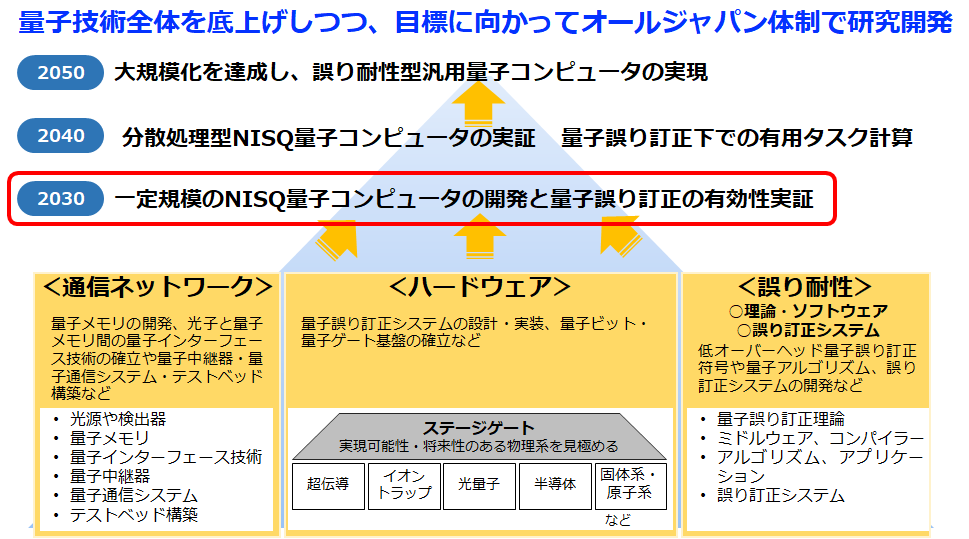

本研究開発プロジェクトは,超伝導量子ビットから中性原子まで多岐にわたる量子ビット実現方式にアジャイルに対応するエラー訂正システムの実現と、超伝導量子ビット向けの小型かつ省電力な量子ビット制御装置の実現である。本ムーンショット目標6の2050年までの目標は,大規模な誤り耐性型汎用量子コンピュータの実現である。本研究開発プロジェクトにおいては、上位に位置する中規模量子ビット間の通信ネットワーク、最上位の量子ビットハードウェアとの組み合わせにより、100万量子ビットまで対応可能なエラー訂正システムならびに量子ビット制御装置を実現可能にする技術の研究開発を行う。 |

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

||||||

|

|

|

|

|||||||||||||||

|

|

|

|||||||||||||||

|

|

|

|

|

|||||||||||||||

|

|

|

| 【公開シンポジウム等での報告】 *JST ムーンショット目標6 公開シンポジウム2023 小林プロジェクトマネージャーから2023年3月28日に報告した際のスライド ----------------- こちら |

| このページのTopへ |

| 課題推進者向け情報 |

| ムーンショット型研究開発事業 JST申請の各種様式等 (公開サイト) | ||

| * プロジェクト関係者向け 各種様式等情報 | --- こちら | |

| グラント番号: JPMJMS226A |

||

| 成果の公表に関する様式 | ||

| PMの実施管理に関する様式 (会議開催 | ||

| PMの実施管理に関する様式 (実施規約) | ||

| 知的財産権管理に関する様式 | ||

| * ロゴマークに関すること | --- こちら | |

| *委託研究開発契約事務処理説明書関連 (大学) --- 令和6年版 --- | --- こちら | |

| *委託研究開発契約事務処理説明書関連 (企業) --- 令和6年版 --- | --- こちら | |

| 学会/セミナー開催情報 | ||

| * 情報学シンポジウム -量子コンピューティングの展開 2023年1月23日開催 (終了) | --- こちら | |

| 主催:日本学術会議情報学委員会 | ||

| プレゼンテーション資料が公開されました。 | --- こちら | |

| * 量子コンピューティングシステムの技術開発の現状と将来展望 2023年1月25日開催 (終了) | --- こちら | |

| 主催:電子情報通信学会東海支部 | ||

| * JST ムーンショット目標6 公開シンポジウム 2023年3月28日開催 (終了) | --- こちら | |

| * Kobe Quantum Error Correction Symposium 2024年1月23日開催 (終了) | --- こちら | |

| 主催:理化学研究所 | ||

| * JST ムーンショット目標6 公開シンポジウム 2024年3月27日開催 (終了) | --- こちら | |

| Qubecsプロジェクト関係者限定情報 (第1パスワードが必要です) | --- こちら |

| 各種資料 課題推進者専用BOX フォルダへのリンク |

| Qubecs パワーポイントのテンプレート 及び Qubecs 各種ロゴ | --- こちら | |

| * ロゴご使用の際には、縦横比の維持をお願いします。 | ||

| Qubecs 内部会議等連絡事項 | ||

| * 第一回Qubecs全体会議 (2022年10月25日開催@京都工芸繊維大学) | --- こちら | |

| * 第二回Qubecs全体会議 (2023年2月27日、28日開催@那覇) | --- こちら | |

| * 第三回Qubecs全体会議 (2023年6月30日@京都工芸繊維大学) | --- こちら | |

| * 第四回Qubecs全体会議 (2023年9月11日@札幌) | --- こちら | |

| * 第五回Qubecs全体会議 (2023年11月29日@理研・神戸) | --- こちら | |

| * 第六回Qubecs全体会議 (2023年3月29日@JST・市ヶ谷) | --- こちら | |

| 外部研究機関との会議等 | ||

| * Leti online 会議 (2023年4月5日開催) | --- こちら | |

| JSTムーンショット目標6 公開シンポジウム等 | ||

| * キックオフシンポジウム(2022年11月18日開催@京都工芸繊維大学) | --- こちら | |

| * Workshop on April 14, 2023 | --- こちら | |

| * JSTムーンショット目標6公開シンポジウム(2023年3月28-29日開催@東京) | --- こちら | |

| * 国際シンポジウム(2023年7月18-20開催予定) | --- こちら | |

| * JSTムーンショット目標6公開シンポジウム(2024年3月27日開催@東京) | --- こちら | |

| 量子コンピューティング関連外部シンポジウム等 | ||

| * 第16回情報学シンポジウム 講演スライド | --- こちら | |

| 学会等技術動向調査(フォルダ) | --- こちら | |

| * ISSCC 2023におけるCryo-CMOS及びQuantum-Computing関連発表事前調査 | ||

| * 近年(2008~2022)のIEDMにおけるCryo-CMOS及びQuantum-Computing関連発表動向調査 | ||

Copyright © 2022-2026 QUBECS. All rights reserved